Hardware for IoT

Hardware For Internet of Things (IoT) Research

Driving revolutionary hardware design for the internet of trillion things.

The Link Lab is developing the next generation of IoT and CPS hardware to address key issues constraining implementations for low power networks and sensor nodes including power management, wireless communications, sensing, and control. A full “circuits to applications” approach will enable greater real-time understanding of the world around us through distributed and ubiquitous sensing through IoT systems that are reliable, efficient, unobtrusive, inexpensive and scalable while maintaining security. In the near-future, the internet of a trillion things will be the endpoints of our connected world impacting infrastructure, healthcare, autonomous systems, smart cities, manufacturing, logistics, financial services, and more.

RESEARCH PROJECTS

Asynchronous Stream Processing

MIRCEA R STAN | RAHUL SREEKUMAR | TOMMY TRACY II

The idea of an end to end asynchronous system is of great interest for ultra low power applications where there is a clear trade-off between power and accuracy. Stochastic computing when implemented asynchronously proves to be an innovative solution towards lesser hardware and silicon footprint. READ MORE

PUBLICATIONS

TOWARDS ON-NODE MACHINE LEARNING FOR ULTRA-LOW-POWER SENSORS USING ASYNCHRONOUS Σ Δ STREAMS ; Patricia Gonzalez-Guerrero, Tommy Tracy II, Xinfei Guo, Rahul Sreekumar, Marzieh Lenjani, Kevin Skadron, Mircea R Stan; ACM Journal on Emerging Technologies in Computing Systems (JETC)

ASYNCHRONOUS STOCHASTIC COMPUTING; PATRICIA GONZALEZ-GUERRERO, Mircea R Stan; 2019 53rd Asilomar Conference on Signals, Systems, and Computers

AI-RISC: Scalable AI processor for IoT edge

MIRCEA R STAN | KEVIN SKADRON | ASHISH VENKAT

AI-RISC is a scalable and flexible processor architecture focussing on hardware/software codesign. AI-RISC augments the open-source RISC-V processor with hardware AI functional units (AFU) along with ISA extensions which directly target these AFUs. AI-RISC is a system-level solution towards the problem of efficient AI hardware at the edge of IoT. READ MORE

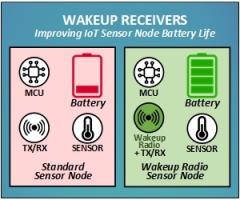

Ultra-Low Power Wakeup Receivers

The Robust Low-Power VLSI group contributes to research on ultra-low power "wakeup" receivers enabling energy-efficient IoT networks. These “always-on” radios increase battery lifetime by acting as wireless event-driven notifiers signaling a sensor node to wake up from sleep mode, all while consuming a million times less power than your cell phone. READ MORE

PUBLICATIONS

A −76DBM 7.4NW WAKEUP RADIO WITH AUTOMATIC OFFSET COMPENSATION, J. Moody et al., 2018 IEEE International Solid - State Circuits Conference - (ISSCC)

A MULTICHANNEL, MEMS-LESS −99DBM 260NW BIT-LEVEL DUTY CYCLED WAKEUP RECEIVER, A. Dissanayake, H. L. Bishop, J. Moody, H. Muhlbauer, B. H. Calhoun and S. M. Bowers, 2020 IEEE Symposium on VLSI Circuits

Fully Autonomous SoC Synthesis

Complex and diverse System-on-Chips (SoCs) are the under-the-hood enablers for today's ubiquitous Internet of Things (IoT). Manually designing them demands years of expertise and several thousands of person-hours. To enable the rapid generation of IoT hardware, we are developing a no-human-in-the-loop, open-source tool to create the SoC in 24 hours. READ MORE

PUBLICATIONS

MEMGEN: AN OPEN-SOURCE FRAMEWORK FOR AUTONOMOUS GENERATION OF MEMORY MACROS, Sumanth Kamineni, Shourya Gupta, Benton H. Calhoun, in IEEE Custom Integrated Circuits Conference (CICC), 2021

AN OPEN-SOURCE FRAMEWORK FOR AUTONOMOUS SOC DESIGN WITH ANALOG BLOCK GENERATION, T. Ajayi, Kamineni, S., Cherivirala, Y. K., Fayazi, M., Kwon, K., Saligane, M., Gupta, S., Chen, C. - H., Sylvester, D., Blaauw, D., Dreslinski, Jr, R., Calhoun, B., and Wentzloff, D. D. , in 28th IFIP/IEEE International Conference on Very Large Scale Integration, Salt Lake City, UT, USA. (Nominated for Best Paper Award), 2020

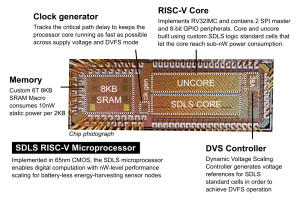

Minimum-Power Digital Logic for IoT Microcontrollers

This project develops a new transistor-level approach to implementing digital logic gates that consume as little power as possible for applications that are critically power-constrained. This new logic gate design is demonstrated in a RISC-V microprocessor chip that achieves 1000x less power than existing commercial solutions. READ MORE

PUBLICATIONS

"A 6–140-NW 11 HZ–8.2-KHZ DVFS RISC-V MICROPROCESSOR USING SCALABLE DYNAMIC LEAKAGE-SUPPRESSION LOGIC," in IEEE Solid-State Circuits Letters, D. S. Truesdell, J. Breiholz, S. Kamineni, N. Liu, A. Magyar and B. H. Calhoun, vol. 2, no. 8, pp. 57-60, Aug. 2019, doi: 10.1109/LSSC.2019.2938897.

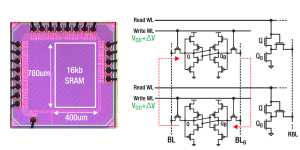

Ultra Low Power SRAM for IoT Applications

Microprocessors store their data in integrated memory circuits that can consume large amounts of power while active. This work develops the lowest-power integrated memory array ever published by using a new bit-cell circuit that consumes almost no power while it is active. READ MORE

PUBLICATIONS

"A 65NM 16KB SRAM WITH 131.5PW LEAKAGE AT 0.9V FOR WIRELESS IOT SENSOR NODES," S. Gupta, D. S. Truesdell and B. H. Calhoun, 2020 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 2020, pp. 1-2, doi: 10.1109/VLSICircuits18222.2020.9162772.

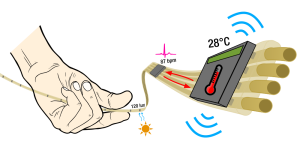

Smart Fiber for Heterogeneous Integrated Sensing

This project leverages advances in materials and textile engineering to build “smart” fiber that integrates a complex network of heterogeneous electronic chips for data sensing, energy harvesting, and communication to enable ultra-compact and low-profile sensing. READ MORE

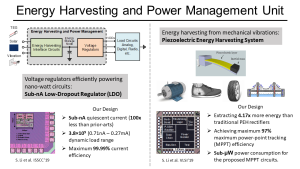

Energy Harvesting and Power Management Unit

Energy harvesting and power management unit is an essential block to extract energy directly from the environment and power IoT devices. In this category, we are showing a low-dropout regulator, which is used to efficiently power nano-watt circuits and a piezoelectric energy harvesting system with over 4× energy-extraction capability. READ MORE

PUBLICATIONS

A 745PA HYBRID ASYNCHRONOUS BINARY-SEARCHING AND SYNCHRONOUS LINEAR-SEARCHING DIGITAL LDO WITH 3.8×105 DYNAMIC LOAD RANGE, 99.99% CURRENT EFFICIENCY, AND 2MV OUTPUT VOLTAGE RIPPLE; Shuo Li, Benton H. Calhoun; 2019 IEEE International Solid-State Circuits Conference (ISSCC)

A PIEZOELECTRIC ENERGY-HARVESTING SYSTEM WITH PARALLEL-SSHI RECTIFIER AND INTEGRATED MAXIMUM-POWER-POINT TRACKING; Shuo Li, Abhishek Roy, Benton H. Calhoun; 2019 Symposium on VLSI Circuits

Tock Operating System for Embedded Systems

Tock OS is an open-source, next-generation embedded operating system that enables system-level safety and strict application-level modularity on tiny memory-constrained embedded systems. The OS design supports RISC-V, and is being used for root-of-trust RISC-V-based silicon that requires stricter safety guarantees while ensuring flexibility. READ MORE

PUBLICATIONS

ENERGY HARVESTING SYTEMS NEED AN OPERATING SYSTEM TOO; Samyukta Venkat, Marshall Clyburn, Bradford Campbell; EnSsys '20: Proceedings of the 8th International Workshop on Energy Harvesting and Energy-Neutral Sensing Systems| November 2020 | Pages 15-21

MULTIPROGRAMMING A 64KB COMPUTER SAFELY AND EFFICIENTLY; Amit Levy, Bradford Campbell, Branden Ghena, Daniel B. Griffin, Pat Pannuto, Prabal Dutta, Philip Levis; SOSP '17: Proceedings of the 26th Symposium on Operating Systems Principles | October 2017 | Pages 234-251